Đề Thi Ôn Luyện Môn Điện Tử Số 2 EPU Đại Học Điện Lực - Miễn Phí Có Đáp Án

Từ khoá: điện tử số 2 ôn thi Đại học Điện lực EPU thi điện tử số câu hỏi ôn thi miễn phí tài liệu điện tử số đáp án điện tử số ôn thi môn Điện tử Số 2 EPU thi Đại học Điện Lực

Số câu hỏi: 158 câuSố mã đề: 4 đềThời gian: 1 giờ

75,166 lượt xem 5,777 lượt làm bài

Xem trước nội dung:

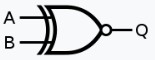

cổng logic dưới hình là cổng:

NAND

NOT

AND

XOR

Bảng sự thật dưới đây là của mạch logic nào

| Đầu vào A | Đầu vào B | Đầu ra Q |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

AND

NAND

NOT

XOR

:cách khai báo nào dưới đây đúng với cổng OR

ENTITY or_gate IS

PORT ( a,b: IN BIT;

q: OUT BIT);

END or_gate;

ENTITY or_gate IS

PORT ( a,b: IN BIT;

q: IN BIT);

END or_gate;

ENTITY or_gate IS

PORT ( a,b: IN BIT,

q: OUT BIT);

END or_gate;

ENTITY or_gate IS

PORT ( a,b: IN BIT;

q: OUT BIT);

END or_gate

[(<00436_C3>)] Điện tử số 2, , Chương 3 Bài tập

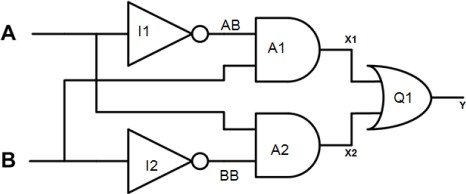

Câu 1 :Khai báo ENTITY nào là phù hợp cho mạch như hình vẽ

|

ENTITY ckt_fig IS PORT(A, B: IN BIT;

Y, X1, X2: OUT BIT);

END ckt_fig;

ENTITY ckt_fig IS PORT(A, B: IN BIT;

Y: OUT BIT;);

END ckt_fig;

ENTITY ckt_fig IS PORT(A, B: IN BIT;

Y: OUT BIT);

END ckt_fig

ENTITY ckt_fig IS PORT(A, B: IN BIT;

Y: OUT BIT);

END ckt_fig;

Bảng sự thật dưới đây là của mạch logic nào

| Đầu vào A | Đầu ra Q |

| 0 | 1 |

| 1 | 0 |

AND

OR

NOT

XOR

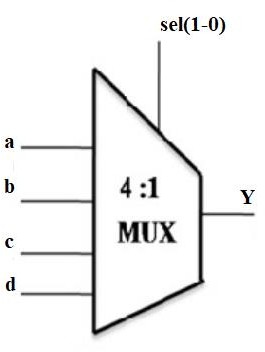

:Cách viết nào sau đây là đúng khi dùng WITH/SELECT/WHEN, WITH sel SELECT

y <= a WHEN"00",

b WHEN"01",

c WHEN"10",

d WHEN OTHERS ;

y <= a WHEN"00",

b WHEN"01",

c WHEN"10",

d WHEN OTHER ;

y => a WHEN"00",

b WHEN"01",

c WHEN"10",

d WHEN OTHER ;

y <= a WHEN"00",

b WHEN"01",

c WHEN"10",

d WHEN"11";

:. Cấu lệnh nào trong phần ENTITY là đúng

| Chức năng | Điều kiện |

| Y=a | Sel=00 |

| Y=b | Sel=01 |

| Y=c | Sel=10 |

| Y=d | Sel=11 |

|

a : in std_logic_vector(2 downto 0);

a: out std_logic_vector;

a : in std_logic;

a : in std_logic_vector;

[(<00436_C4>)] Điện tử số 2, , Chương 4: Thiết kế mạch số trên fpga

Câu 136 Trình tự các bước thiết kế VLSI

System Specification ->Architectural Design ->Functional Design ->Logic Design-> Circuit Design ->Physical Design ->Fabrication ->Packaging

Functional Design ->Logic Design -> System Specification ->Architectural Design-> Circuit Design ->Physical Design ->Fabrication ->Packaging

System Specification -> Logic Design -> Circuit Design -> Architectural Design ->Functional Design ->Physical Design ->Fabrication ->Packaging

System Specification ->Architectural Design->Physical Design ->Fabrication ->Packaging -> Functional Design ->Logic Design -> Circuit Design

cho khai báo như sau

signal x: Bit;

signal y: STD_LOGIC:

Phép gán nào sai

x:=’1’;

x<=’0’

y<=’1’;

y<=’H’;

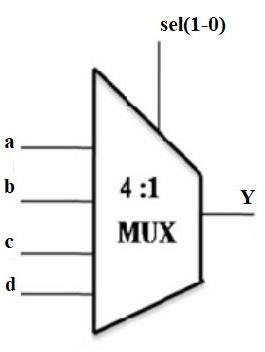

. Câu lệnh nào trong đoạn architecture sai

| Chức năng | Điều kiện |

| Y=a | Sel=00 |

| Y=b | Sel=01 |

| Y=c | Sel=10 |

| Y=d | Sel=11 |

|

architecture rtl of mux4 is begin

Y <= a when (sel = "00") else

b when (sel = ‘1’) else

c when (sel = "10") else

d;

end rtl;

Y <= a when (sel = "00") else

b when (sel = ‘1’) else

c when (sel = "10") else

d;

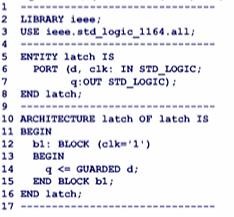

:Trong hình trên Clock là

Xung khởi tạo

Xung đếm

Xung kết thúc

Xung điều kiện

:Trong vd sau, q<=d thực hiện được khi nào

|

clk=’0’

q=1

d=0

clk=’1’

Nếu rst = 1 thì q có giá trị là

Trigger D phát xung dương có tín hiệu Reset tích cực mức cao

3

2

1

0

:Mệnh đề WHEN value 1 | value 2 có nghĩa

điều kiện trong phạm vi từ 0 đến value1 và 0 đến value2

điều kiện của mệnh đề là value1 hoặc value2

điều kiện của mệnh đề là value1 và value2

điều kiện trong phạm vi từ value1 đếnvalue2

: Cách viết nào dưới đây đúng với cổng OR

ARCHITECTURE myarch OF or_gate

IS BEGIN

q<= a OR b;

END myarch;

ARCHITECTURE myarch OF or_gate

IS BEGIN

q<= a AND b;

END myarch;

ARCHITECTURE myarch OF or_gate

BEGIN

q<= a OR b;

END myarch

ARCHITECTURE myarch OF or_gate

IS BEGIN

q<= a OR b;

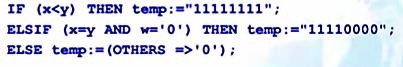

Đoạn chương trình sau sử dụng với lệnh nào

|

ELSIF

THEN

IF

OTHERS

:cách khai báo nào dưới đây đúng với cổng XNOR

ENTITY xnor_gate IS

PORT ( a,b: IN BIT;

q: IN BIT);

END xnor_gate;

ENTITY xnor_gate IS

PORT ( a,b: IN BIT,

q: OUT BIT);

END xnor_gate;

ENTITY xnor_gate IS

PORT ( a,b: IN BIT;

q: OUT BIT);

END xnor _gate;

ENTITY xnor_gate IS

PORT ( a,b: IN BIT;

q: OUT BIT);

END or_gate

:Cách viết nào sau đây là đúng khi dùng WITH/SELECT/WHEN, WITH sel SELECT

y <= a WHEN0,

b WHEN1,

c WHEN2,

dWHEN3;

y <= a WHEN0,

b WHEN1,

c WHEN2,

d WHEN 3,

y <= a WHEN0

b WHEN1

c WHEN2

d WHEN 3;

tất cả đều đúng

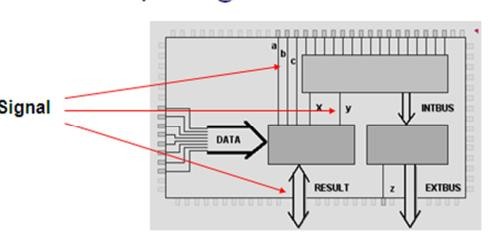

Đâu là internal signal

a,c,y

a,b,c

x,y

a

Bảng sự thật dưới đây là của mạch logic nào

| Input A | Input B | Input C |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

AND

OR

NOT

XOR

Điện tử số 2, , Chương 4: Thiết kế mạch số trên fpga

Câu 1

Ưu điểm của việc thiết kế mạch sử dụng IC có chức năng cố định

Thực hiện thiết kế đơn giản

Kích thước bảng mạch lớn

Dễ sao chép thiết kế

Khó chế tạo được những mạch ứng dụng phức tạp

Khi tín hiệu reset tích cực, các đầu ra của 4 trigger sẽ

Tăng lên 1 mức

Bị xóa về 0

Giảm đi 1 mức

Tín hiệu reset không ảnh hưởng đến 4 trigger

cho khai báo như sau:

signal x: Bit;

signal y: STD_LOGIC:

Phép gán nào đúng

x<=y;

y<=x;

x<=’H’;

y<=’H’;

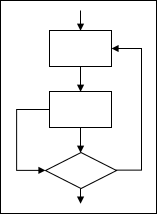

Hình này là kết quả của thiết kế nào trong thiết kế VLSI

|

System Specification

Architectural Design

Functional Design

Logic Design

Đề thi tương tự

3 mã đề 109 câu hỏi 1 giờ

83,084 xem6,385 thi

3 mã đề 106 câu hỏi 1 giờ

68,406 xem5,258 thi

1 mã đề 30 câu hỏi 1 giờ

84,536 xem6,499 thi

7 mã đề 170 câu hỏi 1 giờ

82,002 xem6,303 thi

1 mã đề 24 câu hỏi 1 giờ

68,946 xem5,301 thi

3 mã đề 117 câu hỏi 1 giờ

71,220 xem5,470 thi

3 mã đề 133 câu hỏi 1 giờ

11,791 xem903 thi

5 mã đề 123 câu hỏi 1 giờ

13,567 xem1,037 thi